42 rf front end block diagram

2.2 RF Front End Block Diagram Direct conversion, also known as homodyne or zero-IF conversion, is a natural approach to convert an RF signal directly to ... The Front End block diagram is shown in Figure 1. Receive signals come into the antenna port, are amplified by an LNA low noise mplifier, then RF BPF band pass filtered to remove image components (RF BPA tracks the local oscillator). A mixer stage multiplies the filtered input by a local oscillator to move the input spectrum down to an IF ...

Block diagram of RF front end design ... Radio frequency fingerprinting (RFF) could provide an efficient solution to address the security issues in wireless ...

Rf front end block diagram

Fig. 1. 4G/5G RF front end diagram. • Improve the power efficiency for mmWave FR2 radios; most probably FR2 will be used mainly for downlink in mobile applications [10, 11]. • Increase the number of antennas to 6-8 with the requirement to reach these antennas from different 4G/5G LTE radios which have to coexist with multiple Qualcomm Technologies offers an extensive RF Front End portfolio engineered to deliver integrated solutions for industry-leading RF performance. Our portfolio of power amplifier modules, front-end modules, and diversity receive modules is designed to support virtually all sub-6 GHz and mmWave bands in highly integrated configurations, while ... PIAZZA AND HUANG: 1.57-GHz RF FRONT-END FOR TRIPLE CONVERSION GPS RECEIVER 203 Fig. 1. Block diagram of the complete GPS receiver. from being too low. Surface acoustic wave (SAW) filters for frequencies lower than roughly 100-150 MHz are typically too big and incompatible with our application. As a tradeoff

Rf front end block diagram. The USRP™ B200mini-i delivers a 1x1 SDR/cognitive radio in the size of a business card. With a wide frequency range from 70 MHz to 6 GHz and a user-programmable, industrial-grade Xilinx Spartan-6 XC6SLX75 FPGA, this flexible and compact platform is ideal for both hobbyist and OEM applications. The RF front end uses the Analog Devices AD9364 RFIC transceiver with … 3 shows a typical block diagram of a DSMBGA front-end module with integrated duplexer (FEMiD) and a power amplifier module with integrated duplexer (PAMiD). To provide the high level of integration noted above, several enabling technologies were combined to create a DSMBGA front-end module. By utilizing strip grinding, molded underfill (MUF) and Figure 1. M-MIMO RF front-end block diagram. Wide Operation Bandwidth. ADRF5545A/ADRF5547/ADRF5549 gain characteristics of each device and their respective frequency coverage is shown in Figure 2. Parts are optimized for commonly used cellular bands and aligned with other tuned components used in the same design, such as power amplifiers and ... 2 LTE RF Front-End Design Challenges ... As shown in the simplified diagram below, the key front end components are power amplifiers (PA) and transmit/receive path or duplex filters and switches for band selection or antenna switch module. Figure 1. Simplified Front -End Block Diagram . From UMTS to LTE and beyond, the RF component technologies ...

Low Power Digital I and Q RF Multi-PHY Mode Transceiver www.semtech.com Figure A: SX1257 Block Diagram General Description The SX1257 is a highly integrated RF front-end to digital I and Q modulator/demodulator Multi-PHY mode transceiver capable of supporting multiple constant and non-constant envelope modulation schemes. It is designed Overview. NXP's RapidRF front-end designs for 5G infrastructure integrate a linear pre-driver, RF power amplifier, Rx LNA with T/R switch, a circulator and a bias controller in a compact footprint. They incorporate a coupler for DPD feedback and are to be used with digital pre-distortion. Multi-band Sub-GHz RF Front End www.semtech.com Figure A: SX1250 Block Diagram General Description The SX1250 is a sub-GHz RF Front End device designed to work along with Semtech's SX1302 baseband engine, to design a high-performing LoRa® or LoRaWAN gateway. It covers any frequency band below 1 GHz, making it the RSL10 INTERNAL BLOCK DIAGRAM The block diagram of the RSL10 chip is shown in Figure 1. Figure 1. RSL10 Block Diagram Power Management Unit Antenna DC/DC, LDO Interface (No ext. Balun) Oscillators 32 kHz XTAL 48 MHz XTAL RC Oscillator EXT Clock I/O Bluetooth® Low Energy Radio (Bluetooth5) Arm® Cortex®-M3 processor 32-bit Dual-MAC DSP Core ...

6 Jan 2014 — RF generic front-end block diagram ... In virtually every wireless application from mobile or networking infrastructure (W-LAN / ISM / RFID), ... 1.1 ST25DVxxx block diagram. Figure 1. ST25DVxxx block diagram. LPD. 1. AC0 AC1 V_EH VDCG. 1. GPO Vcc SDA SCL Vss 1.8V VOLTAGE REGULATOR RF INTERFACE 28.5pF tuning capacitance Up to 64Kbits User memory 256 Bytes BUFFER ISO/IEC 15693 PROTOCOL AND CONTROL MEMORY CONTROL DIGITAL UNIT CONTROL ENERGY HARVESTING … Figure 3: Sub-Level Block Diagram Block 1: RF Front End A RF signal is input into the RF front end as shown in Figure 4. In lab, a signal generator produces the RF signal, but in application, an antenna would be used to receive the signal. The signal is amplified in a low-noise amplifier (LNA) to increase the power of the input signal. Guerrilla RF, Inc., a leading manufacturer of high-performance monolithic microwave integrated circuits (MMICs), announced today it has raised more than $7 million in the initial closing of a private placement offering as well as the completion of a reverse merger transaction

04-02-2020 · This article explores the Front Panel and its relationship with the Block Diagram. Learn about the different types of Front Panel objects as well as how to find them on the Controls palette and place them on the Front Panel.

RF Front-End IF Block Back-End Baseband Demodulator ... RF Filter RF Power Amp Mixer RF Low Noise Amp Mixer IF Amp IF Amp IF Filter (Speech, video, data) In Out RF = Radio Frequency IF = Intermediate Frequency LO = Local Oscillator Mixer = Frequency Up- or Down-Converter Figure 1-2: Cell-phone block diagram. 1-1 HISTORICAL TIMELINE 3 devices ...

Front End Block Diagram CA the Three Bands LB -699 to 960 MHz MB -1428 to 2170 MHz HB -2300 to 2690 MHz J. Young "arrier Aggregation, Quantifying Front End Losses," IWPC Chicago Meeting Sept. 16, 2014 2, 3, 4G Module LB GGE MB GGE B1 B4 B25 B3 B8 B20 B26 B12 PA Bias and Control MIPI Interface Switch Bias and Control Load

Integrating more functions into a front-end module (FEM) or filter modules helps to simplify the RF design, as shown in the next block diagram. (A bonus? Integrating the right filter technology inherently helps manage the coexistence issues we discussed earlier, as well as thermal challenges.)

Block diagram of a superheterodyne receiver. The RF front end consists of the components on the left colored red. In a radio receiver circuit, the RF front end is a generic term for all the circuitry between a receiver's antenna input up to and including the mixer stage.

The RF front end contains a number of components that work together to ensure signal integrity throughout the signal's bandwidth. This includes preparing a signal for transmission, as well as receiving and demodulating a signal received on the Rx side. The functional block diagram below shows the general topology of an RF front end.

A Block Diagram of the GPS Orion receiver design appears in Figure 1. The GPS Orion receiver board com-prises the following components:- GP2015 ultra-miniature GPS RF front-end IC, including:-- RF input bandpass filter and +5V DC active antenna supply DW9255 GPS band-definition SAW filter, supplied by Dynex Semiconductor (www.dynexsemi.com).

10 Jun 2021 — Block Diagram of Receiver RF Front End. Oscillators are found in all most every modern wireless communications, radar and remote sensing ...

Basic block diagram of an RF vector network analyzer . The block diagram of a basic two port vector network analyser is shown above. This shows the high level blocks needed for a typical VNA. The VNA has precision connectors on the front panel of the unit itself and then precision cables are used to connect these to the device under test.

Below is a general block diagram for GPS functionality in a device. From the antenna looking into GPS receiver, the ESD device protects the RF front-end against ESD hazards coming from ANT when it makes contact with the external environ-ment. In modern wireless handheld systems, 8 kV contact dis-

by C Zhang · 2009 · Cited by 2 — A schematic diagram of the integrated reconfigurable PA topology is shown in Figure 4.38. The driver amplifier unit is comprised of two amplifiers. The unit has ...

Pasternack's library RF and microwave block diagram are designed to provide engineers and designers with examples of common RF systems schematics while illustrating the RF products and where they fit into the system's design.

4.2 Block Diagram The Avnet Qorvo 2-Channel RF front-end 1.8 GHz (AES-LPA-QRF1800-RVS-G) is a two channel Frequency Division Duplex (FDD) RF front end operating in LTE Band 3. Channel 1 and Channel 2 topologies, shown in the diagram below, are identical. The frequency plan for the two channels are symmetrical as summarized below.

RF tuning & amplification: This RF stage within the overall block diagram for the receiver provides initial tuning to remove the image signal. It also provides some amplification. There are many different approaches used within the RF circuit design for this block dependent its application. The electronic circuit design presents some challenges.

1FEATURES APPLICATIONS DESCRIPTION CC2590 BLOCK DIAGRAM PA Logic Bias 15 7 2 3 4 11 LNA 5 6 BIAS HGM RF_P RXTX RF_N PAEN EN BALUN ANT CC2590 www.ti.com.....SWRS080-SEPTEMBER 2008 2.4-GHz RF Front End, 14-dBm output power

Label the components of a generic radio block diagram. – Explain the path that an RF signal ... They are used extensively in the front end of a radio.20 pages

11-04-2015 · Front end amplifier and tuning block: Signals enter the front end circuitry from the antenna. This circuit block performs two main functions: Tuning : Broadband tuning is …

RF front-end block diagram. The matching network of CC2510 has been designed in a symmetric fashion to avoid any delays and lags. The RF front end consists of COTS components which have been selected according to certain design requirements. The LNA, PA, and RF switches were tested individually for compliance.

high performance RF front end for low-power and low-voltage wireless applications in the 2.4-GHz band. Its single-ended RF input and output make it compatible with any manufacturer's transceiver if appropriate external parts are used. When a transmit/receive (T/R) switch and a balun are used, it can interface with existing and

FUNCTIONAL BLOCK DIAGRAM Figure 1. GENERAL DESCRIPTION The AD9361 is a high performance, highly integrated radio frequency (RF) Agile Transceiver™ designed for use in 3G and 4G base station applications. Its programmability and wideband capability make it ideal for a broad range of transceiver applications.

SIM960 Block Diagram SIM960 PID Controller The low-noise front end brings better performance to noise sensitive applications including laser power and wavelength stabilization, cryogenics, scanning probe microscopy, and others.

Download scientific diagram | (a) Simplified block diagram of the RF front-end. (b) Frequency plan. from publication: A 900-MHz transceiver chipset for two-way paging applications | A 900-MHz ...

The RF front end is generally defined as everything between the antenna and the digital baseband system. For a receiver, this "between" area includes all the filters, low-noise amplifiers (LNAs), and down-conversion mixer(s) needed to process the modulated signals received at the antenna into signals suitable for input into the baseband analog ...

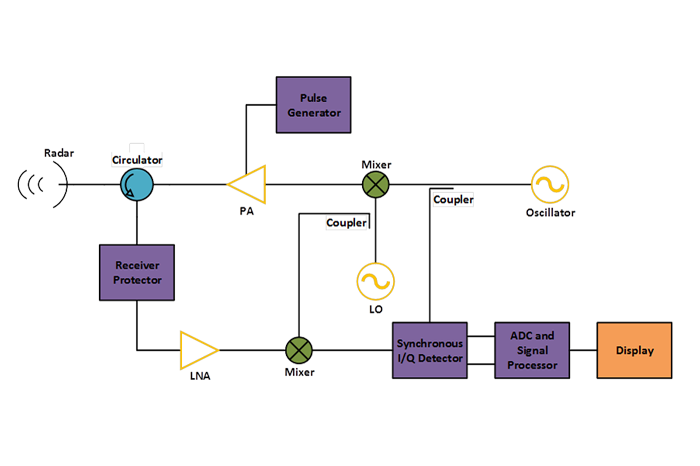

Modeling RF Front End in Radar System Simulation. In a radar system, the RF front end often plays an important role in defining the system performance. For example, because the RF front end is the first section in the receiver chain, the design of its low noise amplifier is critical to achieving the desired signal to noise ratio (SNR).

The figure-2 depicts basic block diagram of 5G cell phone architecture. As shown the architecture include baseband part, digital RF interface such as DigRF, ADC/DAC and RF Transceiver. The basic components are same in the 5G phone except antenna array is used instead of one antenna to support massive MIMO and beamforming.

A tuned radio frequency receiver (or TRF receiver) is a type of radio receiver that is composed of one or more tuned radio frequency (RF) amplifier stages followed by a detector (demodulator) circuit to extract the audio signal and usually an audio frequency amplifier. This type of receiver was popular in the 1920s. Early examples could be tedious to operate because when tuning in …

Below is a non-exhaustive list of Qorvo RF front-end components and block diagrams for FDD and TDD small cell applications. Figure 6. Small cell FDD and TDD block diagrams. Table 1 . Learn to solve network congestion & efficiency with Small Cells. Download Now >

PIAZZA AND HUANG: 1.57-GHz RF FRONT-END FOR TRIPLE CONVERSION GPS RECEIVER 203 Fig. 1. Block diagram of the complete GPS receiver. from being too low. Surface acoustic wave (SAW) filters for frequencies lower than roughly 100-150 MHz are typically too big and incompatible with our application. As a tradeoff

Qualcomm Technologies offers an extensive RF Front End portfolio engineered to deliver integrated solutions for industry-leading RF performance. Our portfolio of power amplifier modules, front-end modules, and diversity receive modules is designed to support virtually all sub-6 GHz and mmWave bands in highly integrated configurations, while ...

Fig. 1. 4G/5G RF front end diagram. • Improve the power efficiency for mmWave FR2 radios; most probably FR2 will be used mainly for downlink in mobile applications [10, 11]. • Increase the number of antennas to 6-8 with the requirement to reach these antennas from different 4G/5G LTE radios which have to coexist with multiple

Comments

Post a Comment